الخلاصة: لFPGA اختبار البرمجيات اختبار المحاكاة العملية وعدم كفاية الاختبار البدني والاختبار الآلي المقترحة محاكاة البيئة المادية على أساس حالات الاختبار، اختبار Testbench محاكاة لعملية تحليل، وتشكيل إشارة الإرسال FPGA يمكن استخدامها لاختبار بدني، التي يتم تحويل هذه الإشارة المحرك إلى إشارة الاختبار الفعلي يتم تطبيقه على شريحة FPGA، واستجابة قياس من مجموعة شرائح FPGA، مؤتمتة اختبار إعمال المادي للFPGA. يتم التحقق من التصميم والهندسة المعمارية، وحققت نتائج جيدة باستخدام منصة التحقق الفعلي لبيئة الاختبار الآلي.

TP311.11

A

10.16157 / j.issn.0258-7998.173548

شكل الاقتباس الصيني: قاو هو جين تاو، قوية غطاء داخل الجبهة، تشاو قانغ. FPGA التصميم الآلي بيئة اختبار على أساس Testbench البدنية التكنولوجيا الالكترونية، 2018،44 (4): 48-51.

الإنجليزية شكل الاقتباس: قاو هو جين فنغ Erqiang، تشاو قانغ، تصميم FPGA البدنية بيئة الاختبار التلقائي استنادا Testbench . تطبيق تقنيات الالكترونية، 2018،44 (4): 48-51.

0 مقدمة

مع التوسع المستمر لحجم تصميم FPGA، FPGA تصميم البرمجيات بسبب نوعية المشاكل التي تسببها أكثر وأكثر وضوحا، أصبح عامل مهم يؤثر على نوعية المعدات . الاختبار الحالي هو أكثر وسيلة فعالة لحل هذه المشكلة، لذلك، اقترح عدد متزايد من النماذج ونوع المعدات عملية الموافقة على FPGA اختبار البرمجيات المتطلبات الجديدة .

ومع ذلك، تختلف عن التقليدية اختبار FPGA اختبار البرمجيات، لأن حدود بيئة اختبار طرق الاختبار تتطلب الكثير يعتمد على محاكاة وتحليل ، واختبار أجري في الممارسة وغالبا ما يكون مجلس رقاقة واختبار مستوى النظام، قد تكون نتائج الاختبار ثقة منخفضة، ولا يمكن على نحو فعال FPGA تصميم البرمجيات العيوب وجدت . ولهذه الغاية، نقترح الاختبار الآلي إطار استنادا إلى بيانات اختبار منصة Testbench المحاكاة البيئية، ونتائج الاختبار مع موثوقية عالية، ويمكن FPGA تحسين نوعية الاختبار.

1 FPGA الحيوي اختبار نظرة عامة

1.1 FPGA مبدأ ديناميكية بيئة الاختبار

وقد تم تجهيز النموذج الحالي FPGA الطرق الرئيسية من نوع عملية الاختبار بما في ذلك التحقق من التصميم والمحاكاة وظيفية، والمحاكاة على مستوى البوابة، والمحاكاة توقيت، تحليل توقيت ثابت، والتحقق من المنطق التكافؤ والاختبارات البدنية. التي محاكاة وظيفية، والمحاكاة على مستوى البوابة، والمحاكاة توقيت واختبارات اللياقة البدنية واختبار ديناميكية، والحاجة إلى اختبار وفقا للشروط المنصوص عليها في FPGA البيئة الخارجية تشغيل إجراء الاختبار، وفقا لكائنات الاختبار المختلفة، مثل هذه البيئات يمكن تقسيمها إلى محاكاة واختبار بيئة بيئة اختبار المادية.

مع بيئة اختبار مضاهاة، حالات الاختبار أن تستند إلى إشارات بيانات الاختبار التي تم تعيينها إلى قيم مختلفة في أوقات مختلفة تشكيل ملف منصة اختبار Testbench، ردا على أداة اختبار قياس عن طريق المحاكاة FPGA الناتجة عن اقتناء والحكم التلقائي، والتي تشكل نتائج الاختبار .

عند استخدام بيئة اختبار المادية، وتميل إلى بيئة اختبار نظام بناء، وتشغيل مع FPGA ودوائر هامشية والأجهزة والبيانات حافز من خلال واجهة حافلة الخارجية يتم توفيرها، ثم واجهة لعرض نتيجة استجابة بواسطة المخرج حافلة، والتحليل اليدوي والحكم، وتشكيل نتائج الاختبار .

1.2 FPGA صفة ديناميكية اختبار

اختبار دينامية لأن النظام تنفيذ اختبار تحت الاختبار قيد التشغيل، ليعكس بشكل أدق سلوك وقت التشغيل الفعلي للنظام، وأصبحت واحدة من أهم الوسائل لاختبار في اختبار التكنولوجيا. FPGA طريقة اختبار ديناميكية يشيع استخدامها اختبار والجمع بين اختبار المحاكاة المادية، عن طريق إجراء اختبار متطلبات FPGA تغطية القضية، وجدت عيوب ذات الصلة، مقارنة مع اختبار ثابت، نتيجة الاختبار هي بديهية، ومزايا تغطية أعلى.

ومع ذلك، FPGA اختبار ديناميكية، وهناك بعض أوجه القصور في مهمة نموذج اختبار الحالية على نحو متزايد بارزة ، بما في ذلك: (1) محاكاة تختبر تعتمد أيضا على أداء أداة المحاكاة، (2) عن طريق استخدام محاكاة اختبار التغطية الملكية الفكرية الأساسية وأسباب أخرى لا يمكن أن تكون مضمونة بالكامل؛ (3) بيانات الاختبار المادية للنظام، ولكن ليس للإشارة رقاقة.

النظام الحالي هو موثوق بها للغاية طرق الاختبار FPGA ديناميكية باعتبارها وسيلة هامة لاختبار المهمة اختبار نموذج في ممارسة مهنة الهندسة، على الرغم من أنه يمكن العثور على عدد كبير من عيوب الجودة FPGA، ولكن السلبيات المذكورة أعلاه لم تحل، FPGA خطر الجودة المحتملة لا يمكن السيطرة على نحو فعال.

2 تصميم بيئة اختبار الآلي

2.1 المتطلبات البيئية تحليل

من أجل تحسين النظام الحالي من موثوقية عالية ومصداقية كفاءة اختبار FPGA اختبار ديناميكية، تحتاج متطلبات الاختبار الديناميكي لتلبية الاختبار التالي:

(1) اختبار يجب أن تكون قادرة على عكس تماما مدخلات الإثارة والسلوك الناتج من شرائح FPGA، مما يعكس ليس فقط على اختبار مستوى النظام الإثارة بيانات التطبيق، أي بيانات الاختبار من طبقة التطبيقات إلى ضرورة الحد من طبقة نقل الإشارات.

(2) اختبار ديناميكية الهدف FPGA تصاميم حاجة لتشغيل على جهاز حقيقي، بدلا من استخدام FPGA هدف العملية أداة محاكاة بديلة.

اقتناء و(3) تطبيق اختبار الإثارة ديناميكية نتائج الاختبار هي قادرة على تلبية الدقة في الوقت الحقيقي ومتطلبات التصميم FPGA، أي يمكن تطبيقها إشارة الدخل مع دقة عالية لتصميم اختبار FPGA، قادرة على دعم عالية في حين أن FPGA إشارة خرج قياس اكتساب الدقة، علاوة على ذلك، كل من استجابة FPGA في الوقت الحقيقي وللإشارة الإثارة يجب ان تلبي متطلبات النظام .

2.2 الإطار البيئي للبناء

2.2.1 الأشغال

لتلبية احتياجات بيئة اختبار حيوية، تصميم الاختبارات على أساس Testbench البيئة الجسدي من قبل نطاق Testbench للإشارة الاختبار، والوقت الزناد واصف، واحتياجات طبقة انتقال إشارة إلى حل حافزا الاختبار؛ Testbench عن طريق تحويل إشارة إلى إشارة حقيقية ويتم تطبيقها على الدائرة FPGA رقاقة قياس حقيقي حل عملية أصالة نظام الاختبار؛ وصفت Testbench الدائرة تحويل إشارة إشارة حقيقية من الأداء العالي رقاقة FPGA، وردا على الإثارة من دقة حل الاختبار ومتطلبات الوقت الحقيقي. خاص يعمل على النحو التالي: ويمكن الحصول على Testbench تحليل الدلالي للبيانات الاختبار التحفيز. إذا استخدمت هذه البيانات الإثارة للمحاكاة، وبعد تطبيق اختبار لتوزيع إشارة رقاقة كيان FPGA لا يمكن أن تتحقق Testbench الاختبار البدني القائمة. وفي الوقت نفسه، فإن عملية تحليل Testbench قراءة إشارة المرجوة، إشارة خرج من قرأ قياس ويمكن الحصول على FPGA كيان FPGA نتائج اختبار المدى، والنتائج التشغيلية الفعلية مع النتائج المتوقعة ومن ثم المطابقة التلقائية، يمكن أتمتة Testbench أساس من عملية الاختبار.

2.2.2 نظام العمارة

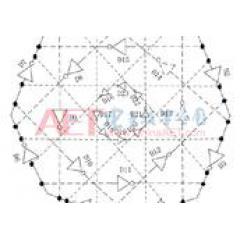

وFPGA الاختبار الآلي يعمل تحت Testbench، مؤتمتة اختبار FPGA بيئة تصميم الإطار هو مبين في الشكل.

بيئة الاختبار وفقا لمتطلبات الوقت الحقيقي للاختبار وتنقسم الى مجموعتين المنصات الرئيسية وتنفيذ منصة جزء، وهو وقت غير الحقيقي عقدة رئيسية الإنترنت، وينفذ عقدة منصة في الوقت الحقيقي.

منصة المضيف الرئيسي لاستكمال التحليل إعداد الاختبار ونتائج الاختبار. وتشمل الاستعدادات إعداد حوافز إعداد اختبار واجهة الاختبار. الإثارة إعداد اختبار يشير إلى المعلومات اختبار الإثارة Testbench عملية تحليل، عملية محددة: بعد تحرير Testbench في منصة الرئيسية، التي تم إنشاؤها بواسطة Testbench الرسمي المعالجة، وحلها في مجال الإثارة النتائج حقلين حقول فئة، كل حقل يحتوي المجال الزمني، دبوس 3 وعنصر دبوس القيم، في نهاية المطاف مع الرسالة إطار بيانات اختبار التحفيز، وإرسالها إلى منصة الإعدام عن طريق رسالة الإطار البيانات إيثرنت. يشير إلى إعداد اختبار واجهة واجهة الطرفية نموذج تصميم FPGA اختبار، والتنسيب، والتوجيه تحميلها على الأداء العالي FPGA (المشار إليها فيما يلي باسم FPGA المستجيب) خلال عملية الانتظار، اختبار FPGA لبنود الاختبار المختلفة ، إنشاء نموذج واجهة من FPGA المحرك على التوالي. تلقي نتيجة اختبار لتحليل البيانات نتيجة الاختبار، وتوليد تقارير الاختبار.

ويمكن اعتبار منصة الإعدام باعتبارها مضاعفة منصة إشارة الإرسال والاستقبال، الصادرة عن سيد Testbench يتلقى تنشيط رسالة الإطار البيانات، وتخزينها في كتلة في DPRAM، عند تلقي الأمر تنفيذ اختبار، رسالة إطار البيانات إلى DPRAM بواسطة المحرك FPGA. المحرك وفقا FPGA إشارة الزناد دبوس، وقيمة إشارة للإشارة في المعلومات في الوقت صفها في DPRAM، إشارة خرج تقاس إلى FPGA، وقراءة إشارة الإخراج التي تم إنشاؤها وفقا لاكتساب عنوان دبوس وتوقيت الشراء FPGA قياسها، ومن ثم جمع يتم إرسال FPGA نتيجة قياس ردا على المعالج عبر DPRAM، وتقديم التقارير في الوقت الحقيقي إلى منصة رئيسية لرصد وتحليل نتائج الاختبار.

2.3 تقنية مفتاح

وبناء على Testbench Testbench بيئة الاختبار الآلي المادية للبيانات الأساسية، وتحويل البيانات عن طريق الإشارة المحرك FPGA، وبالتالي، الأساليب التحليلية والمحرك Testbench FPGA بناء التصميم المادي هي التكنولوجيا الرئيسية لبيئة اختبار الآلي.

2.3.1 المنهج التحليلي Testbench

Testbench هو تنفيذ FPGA تعتمد على البيانات اختبار، FPGA جمعت أيضا محرك نتائج الاختبار. Testbench الناتجة عن الإثارة، يتم تطبيق الإثارة، استجابة لتحديد أن 3 أجزاء . في تنفيذ Testbench تحليل شيدت يشير أساسا إلى مولد الإثارة ردا على تحليل القرار بناء آلية نوع بيئة اختبار من Testbench؛ وتطبيق الإثارة كبيرة لاختبار مثال FPGA (أي DUT، تصميم تحت الاختبار)، لأتمتة البناء المادي لا يتأثر بيئة الاختبار.

Testbench بغض النظر عن بنيات اللغة، يتم تطبيق الإثارة سوف تنتج مجموعة نهائية من عمليات لتنفيذ قيمة محددة لدبوس DUT يعملون في وقت معين، يتم تطبيقه يمكن حلها عملية الإثارة Testbench لضبط الوقت، دبوس، والقيم دبوس، اسمه هذه المجموعة من نطاق الإثارة.

يتم تحديد استجابة في سياق سلسلة من Testbench الإثارة يتم إنشاؤها وتطبيقها على تجسيد، المجال الإثارة، مثل DUT، يفهم هذه العملية أيضا للعب في مجموعة حظة معينة من التشغيل DUT دبوس القيم المكتسبة، يتم حل وقت العملية أيضا ل ، دبوس، دبوس 3 قيمة الميزة، ومجموعة من النتائج لاسم المجال. يختلف من حقل الإثارة، يمكن تعيين قيمة نتيجة الحقول دبوس لتخزين نتائج البيانات المتوقعة هذا الرقم إلى قيمة فارغة، وهذا هو، من دون النتائج المتوقعة، ونتائج الاختبار يمثلها تقرير البشري.

وباختصار، مجموعة من FIG Testbench يمكن حلها في الميدان الإثارة ونتيجة الحقل هو مبين في الشكل 2.

لتحسين دقة من اختبار البيئة والوقت كفاءة التخزين السيطرة ، وحقل نتيجة الحقل الإثارة في لحظة زمنية معينة لمراقبة توقيت ترتيب تحليل نقطة Tickset، شكل والتي تم تعريفها على النحو التالي:

حيث، tickVal يمثل نقطة في الوقت المناسب للإشارة الإثارة يتم تشغيل، drvPinNum لتخزين عدد من النقاط في الوقت نفسه المخصصة للدبابيس، يتم توجيه drvTab إلى تكوين دبوس الجدول مؤشر التكوين دبوس هيكل جدول معين على النحو التالي:

وهكذا، فإن نقطة زمنية هي بنية Tickset يحتوي drvPinNum الإثارة sampPinNum على جمع المسامير والدبابيس، وقيمة كل دبابيس عنوان مدرجة ايضا.

Testbench عدد وافر من النقاط الزمنية المدرجة، معا تشكل حالة اختبار، وبالتالي يمكن تعريفها بأنها بنية حالة اختبار، على الشكل التالي:

TickNum Tickset يحتوي على التكوين في القضية، مؤشر المتغير tickPoints يظهر تكوين محددة نقطة مجموعة Tickset تحكم توقيت.

نوع واحد من بيئة التشغيل الآلي للاختبار مصمم لتحسين كفاءة الاختبار، وتحقيقا لهذه الغاية، قد يكون كل ولدت Testbench التحليل الأول، وتوليد حالات الاختبار Caseset والتنفيذ دون انقطاع من حالات الاستخدام ضمن مجموعة من حالات الاختبار. يتم تعريف شكل Caseset على النحو التالي:

Testbench تصميم برامج التحليل، وفقا لشكل ملف بروتوكول اتفاق بعد تحليل كافة Testbench الشكل، ومجموعة من حالات الاختبار أرسلت في نهاية المطاف إلى منصة الإعدام Caseset، وحدة المعالجة المركزية يكتب في DPRAM، والمحرك لقراءة FPGA، التكوين.

2.3.2 المحرك تصميم FPGA

يتم قياس FPGA واجهة محول المحرك وحدة محول FPGA وبيئة اختبار، وتحويل كامل الدائرة الرئيسية إشارات البيانات Testbench، يلعب دورا محوريا في بيئة الاختبار الآلي. وحدة رئيسية والعلاقة الداخلية نقل المعلومات هو مبين في الشكل (3).

المحرك FPGA يقرأ رسالة البيانات DPRAM Testbench تنشيط، ويوزع حقل نتيجة الحقل الإثارة، وقيم تحكم توقيت المشار إليها عملية مكافحة المجالات اثنين.

الإثارة وحدة تحليل الحقل يقرأ البيانات DPRAM الإثارة عنوان FPGA دبوس ليتم تطبيقها، وقيمة الإثارة ، ثم مؤشر وFPGA البيانات دبوس مغلق من البيانات وحدة تعيين عنوان وصوله في الوقت الإثارة بعد بيانات الإثارة الزناد المحدد من قبل دبوس إخراج قيد الاختبار إلى FPGA.

وحدة ناتج الحقل إعراب يقرأ دبابيس عنوان المطلوبة للحصول على نتيجة اكتساب DPRAM، القيمة المتوقعة من النتيجة، من خلال البيانات عنوان وحدة توزيع الخرائط دبوس، وقت وصول عندما جمع وإعادة قراءة البيانات عنوان من اقتناء وحدة تخصيص المخزن المؤقت المقابلة قيم البيانات، وبالمقارنة مع القيمة المتوقعة نتيجة المكتسبة في DPRAM، في الوقت الذي استنتاج ينتقل إلى وحدة تحكم لتحميل لDPRAM الانترنت مع نتائج الاختبار الفعلي.

وحدة التحكم توقيت هو السيطرة المركزية من المحرك FPGA، من جهة، والوقت للقراءة وصفها في DPRAM، وهي المرة التي حصلت عليها حساب لFPGA المحرك الناتج المدخلات الزناد الفعلي بواسطة جهاز التحكم العداد واكتساب تمكين الإثارة، من أجل تحقيق إشارة FPGA في الوقت الحقيقي التحكم في النقل، ومن ناحية أخرى، من خلال قراءة عدد من حالات الاختبار في DPRAM، وعدد من الحقل الإثارة الاختبار، وعدد من الدبابيس يؤدي إشارات عدد من المجالات، كل مجال في نقاط زمنية مختلفة، مختلفة اختبار اختبار إدارة الوقت حالة تقدم نتائج في مجال البيانات الإثارة المجال الزمني، التكوين دبوس، أساس لحقل الإثارة تحليل وحدة وحقل نتيجة تحليل وحدة دبوس وتوزيع البيانات.

وعلاوة على ذلك، يتضمن المحرك مزيد من FPGA التكوين إدخال دبوس مجموعة من FPGA سيد البرمجيات واجهة النمذجة منصة الاختبار، ومجموعات دبوس الانتاج وINOUT مجموعة دبوس، لاستقبال وحدة تعيين عنوان مع إدارة البيانات.

2.4 الأجهزة ونشر البرامج

تتكون الآلي بيئة اختبار حيوية من جزأين منصات أجهزة الكمبيوتر الشخصية الرئيسية ومنصة الإعدام الرقيق، التي تعمل على منصة الكمبيوتر المضيف دون الحاجة لتنفيذ تصميم الأجهزة الخاصة، منصة الإعدام بما في ذلك FPGA 3 جزء X86CPU، DPRAM والمحركات، والتي X86CPU من خلال DPRAM المحرك FPGA البيانات والاتصالات التصميم باستخدام طريقة التواصل DPRAM التقليدية.

البرمجيات، وPC سيد منصة نشر برامج التحليل Testbench، لحل Testbench Caseset شكل مجموعة الاختبار؛ FPGA اجهة النمذجة اختبار البرمجيات نشر، نفذت المحرك FPGA وتقاس عن طريق خلط المستجيب FPGA FPGA بيئة تطوير متكاملة ISE دبابيس تكوين اتصال، توليد تلقى لينة من خلال الرصد والإبلاغ وعرض البيانات نتيجة تنفيذ اختبار، وتوليد تقارير الاختبار؛ إعدام آلة أقل منصة X86CPU تشغيل في الوقت الحقيقي نظام التشغيل VxWorks 5.5 البيانات التنفيذ والاختبار لاختبار قيادة التوزيع والتغذية الراجعة الفورية.

3 التجارب والتطبيقات

وبناء على طريقة تصميم أعلاه، ووضع تصميم محاكاة FPGA التجسيد المادي مع بيئة اختبار النموذج الأولي، تضم Testbench برنامج محلل، والنمذجة البرمجيات واجهات البرامج FPGA الأساسية بتوزيع الملف في شكل مجموعة Caseset Testbench؛ XC7VX690T يعملن المحرك FPGA، وبيانات التصميم الذي تحويل إشارة المنطق ولوحة التصحيح وتقاس يشابك الخارجي FPGA رقاقة. منصة محاكمة FPGA نوع معين من الملاحة عبر الأقمار الصناعية وبرامج الاتصالات الاختبار، مقارنة مع "+ نظام المحاكاة" وضع الاختبار، تحسن إلى حد كبير اختبار الكفاءة.

4 خاتمة

Exploringly هذه الهدايا ورقة نوع من بيئة الاختبار الآلي على أساس محاكاة منصة اختبار لFPGA اختبار البرمجيات واختبار محاكاة لتعويض أوجه القصور في الاختبار الحقيقي الحالي موجود للتحقق من إطار التصميم من خلال العينية النموذج الآلي بيئة اختبار، فقد بينت النتائج أن بيئة اختبار مع تغطية عالية الاختبار، ومزايا الكفاءة اختبار ليكون الأمثل في مشاريع لاحقة يمكن أن تستخدم كأداة رئيسية لممارسة FPGA اختبار الهندسة.

مراجع

قاو هو جين تاو، ليو يوان ليو تسي يي .DO-254 معيار التحقق من صحة وعملية التحقق تحليل الطيران مواصفات والجودة، 2014 (2): 10-13.

Liuzai يي، ليو تشانغ تشنغ. واستنادا FPGA اختبار اختبار البرمجيات والتكنولوجيا التكنولوجيا الالكترونية، 2011،37 (5): 28-30.

بحث تشو شان يانغ ياون، وانغ جينبو. رحلات الفضاء عالية الموثوقية اختبار التكنولوجيا FPGA تقنية الكمبيوتر والتنمية، 2017،27 (3): 1-5.

رسوم يانان، تشو هوى، وقال تشو ويى جيى .FPGA برامج الحاسوب الآلي وتصميم منصة التحقق والممارسة قياس الكمبيوتر والتحكم، 2016،24 (5): 139-142.

LEMON R، COULTER B، ARCHIBALD S، وآخرون al.Interface تنمية محول اختبار وصيانة باستخدام / عزل محطة اختبار التلقائي الاستمرارية في الاختبار على نطاق واسع .Autotestcon 2009 IEEE 2009: 107-112.

JUSTIN J، ليندستروم L، JAIN A.Using المكونات في نموذج لتبسيط وتعزيز قدرات أكل اختبار البرمجيات .Autotestcon، 2012 IEEE 2012: 105-107.

وانغ بنغ، وليو وان، ليو روي وهلم جرا. وبناء SystemVerilog منصة الاختبار التي يمكن إعادة استخدامها التكنولوجيا الالكترونية، 2015،41 (2): 61-64.

قاو هو تشنغ يونيو، تشاو قانغ .FPGA إطار التشغيل الآلي للاختبار محاكاة على مستوى اللوحة لتصميم البيئي الالكترونيات الدقيقة وعلوم الحاسوب، 2017،34 (12): 94-98.

الشمس Xiurui .FPGA برنامج التحقق من تصميم والأجهزة شارك في محاكاة في طريقة الاختبار جامعة نانتونغ (العلوم الطبيعية)، 2016،15 (3): 41-44،66.

وانغ Xiaogeng على أساس مؤتمتة بالكامل تصميم شركة نفط الجنوب الرقمي والتحقق من تنفيذ VHDL شيان: شيان جامعة العلوم الالكترونية والتكنولوجيا، عام 2016.

يي مين Sushu جينغ جي وي، وما إلى ذلك وبناء على ارتفاع السرعة FPGA لمرة ونظام أخذ العينات بديلة التكنولوجيا الالكترونية، 2015،41 (1): 71-74.

المادة المال، والملك بينغ جيانغ بن بطاقة وحدة المعالجة المركزية القائمة على التحقق رقاقة منصة UVM الالكترونيات الدقيقة وعلوم الحاسوب، 2016،33 (6): 37-40.

جيان تشونغ يانغ لو في الوقت الحقيقي الحصول على البيانات ونظام النقل بسرعة عالية علوم الكمبيوتر، 2016،43 (S2): 604-606.

الوقف بو، وتشانغ يونغ، كان، وما إلى ذلك تحقيق استنادا FPGA أربعة RAM . مجسات والأجهزة التقنية، 2017 (1): 34-37.

الكاتب المعلومات:

قاو هو جين تاو، قوية غطاء داخل الجبهة، تشاو قانغ

(المعهد الوطني للالصين الوطنية ايرو التكنولوجيا، بكين 100083، الصين)